Nvidia priorise les designs dual-die de sa série Blackwell

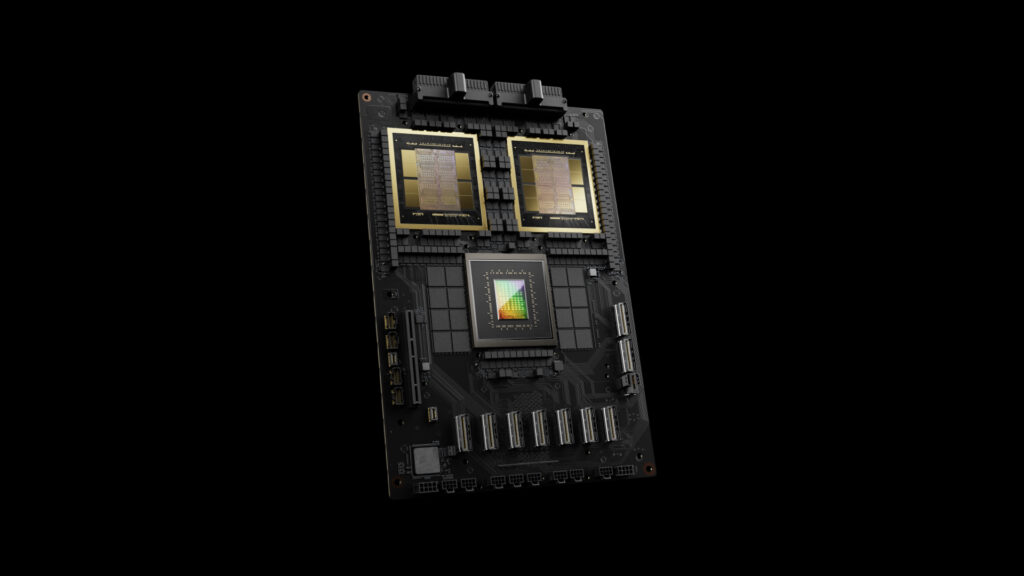

Demande pour les nouveaux designs Blackwell à double puce de Nvidia aurait dépassé celle des designs à simple puce de Nvidia. L’analyste de TF International Securities, Ming-Chi Kuo, rapporte que le géant de la fabrication de GPU d’une valeur de trillions a mis à jour sa feuille de route de l’architecture Blackwell pour donner la priorité aux designs à double puce avec un packaging CoWoS-L. À partir du premier trimestre de cette année, Nvidia se concentrera apparemment sur ses GPU Blackwell de la série 200. Cependant, il est important de noter que cela inclut uniquement les versions multi-puces de la série 200, comme le GB200 NVL72 – les versions à simple puce de la série 200, telles que le B200A, ont été arrêtées.

Nvidia met l’accent sur les designs à double puce

De même, Nvidia prévoit apparemment de donner la priorité aux modèles de série B300 qui tirent parti de plusieurs puces, en particulier le GB300 NVL72. Les variantes de GPU B300 n’utilisant qu’une seule puce auront un rôle de faible priorité dans la fabrication en raison de la demande plus élevée pour les variantes multi-puces. Les modèles de GPU Blackwell haute priorité de Nvidia utilisent la technologie CoWoS-L plus avancée de TSMC. Les modèles B200A arrêtés et les GPU B300 à simple puce utilisent tous deux le CoWoS-S. En raison de ces changements, certains fournisseurs seront particulièrement touchés alors que Nvidia donne la priorité aux designs à double puce. Ainsi, l’emballage CoWoS-L sera nécessaire pour construire ces modèles. Ceux qui fournissent à Nvidia du CoWoS-S seront les plus impactés par la nouvelle feuille de route de Nvidia.

Impact sur les fournisseurs et TSMC

Cependant, TSMC ne sera apparemment pas significativement impacté par ces changements. Le fabricant taïwanais de semi-conducteurs prévoit de donner la priorité au CoWoS-L en tant que solution principale, ce qui est en ligne avec les plans de Nvidia d’utiliser le CoWoS-L comme solution dominante. De plus, la transition de la fabrication du B200 au B300 implique le même processus FEoL, ce qui améliorera l’efficacité de la production et réduira les temps d’arrêt potentiels. TSMC s’attend à ce que l’IA/HPC soit sa principale source de croissance pour 2025.

Les technologies d’emballage CoWoS-S et CoWoS-L sont fabriquées par TSMC. CoWoS-S, ou Chip on Wafer on Substrate avec un interposer en silicium, offre des interconnexions à haute densité et des capacités de tranchées profondes sur une grande zone d’interposer en silicium pour accueillir des composants tels que des chipsets logiques et de la mémoire HBM.

CoWoS-L combine CoWoS-S avec InFO, la technologie Fan-Out Integrate, pour fournir une plus grande flexibilité lors de l’utilisation d’un interposer avec un LSI (Local Silicon Interconnect) ou une puce. Ces ponts sont une partie essentielle de la conception, et c’est pourquoi les GPU Blackwell multi-puces ont pu maintenir leur interconnexion NVLink 10TB/s.

Recevez les meilleures actualités et les critiques approfondies de Tom’s Hardware directement dans votre boîte de réception.

Source : www.tomshardware.com