Samsung prévoit de produire des premiers dispositifs mémoire HBM4 en 2025

Le futur de la mémoire HBM4

Samsung s’apprête à produire ses premiers dispositifs de mémoire HBM4 plus tard cette année, avec des échantillons prévus pour début 2025 selon des sources industrielles citées par nN Elec. Le géant sud-coréen utilisera son processus de fabrication de DRAM de dernière génération en classe 10nm pour fabriquer des dispositifs de HBM4 DRAM ainsi que sa technologie logique en classe 4nm pour produire des matrices de base HBM4, indique le rapport. Après la production des premiers dispositifs de mémoire et matrices de base HBM4 par Samsung, ses usines de mémoire et de logique devront les produire et les assembler, ce qui prendra quelques mois ou plus. Ensuite, Samsung testera ces piles HBM4 en interne avant de les proposer en échantillon à ses principaux clients, notamment les principaux fabricants de processeurs pour l’intelligence artificielle et le calcul haute performance. Samsung a refusé de commenter son calendrier pour la HBM4. La production en masse de la HBM4 par Samsung devrait commencer d’ici la fin 2025, bien qu’il reste à voir quand les produits réels utilisant cette technologie verront le jour.

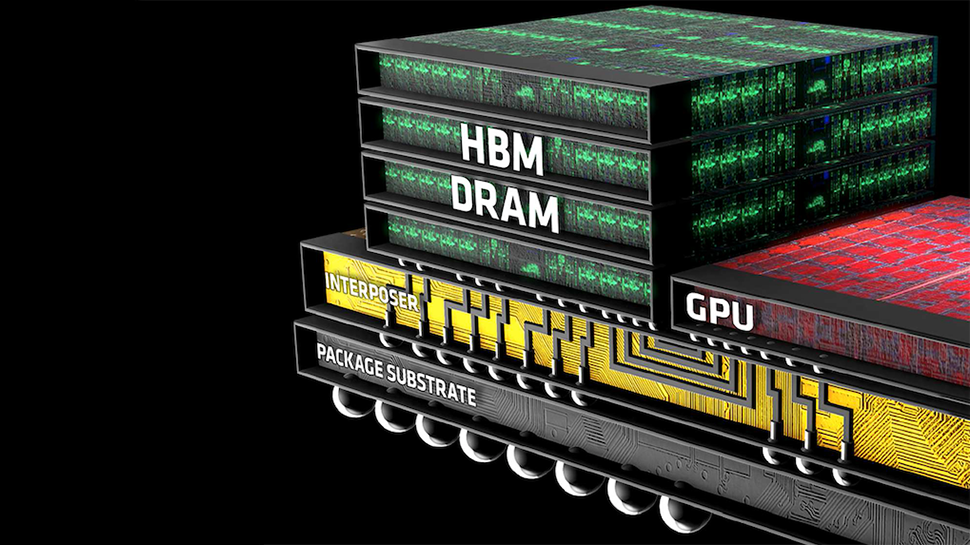

Les caractéristiques de la HBM4

La prochaine norme HBM4 définira des couches de mémoire de 24 Gb et 32 Gb ainsi que des piles TSV de 4, 8, 12, et 16 rangées. Il est difficile de prédire la configuration des premiers modules HBM4 de Samsung, bien que le rapport indique que l’entreprise se concentrerait sur la production en masse de piles HBM4 de 12 rangées au second semestre de l’année prochaine. Les vitesses de ces modules dépendront de plusieurs facteurs, bien que les vitesses préliminairement définies par la JEDEC atteignent jusqu’à 6,4 GT/s.

La concurrence avec SK Hynix et TSMC

Le rival de Samsung, SK Hynix, prévoit également de produire en masse la HBM4 au second semestre de l’année, bien que la date de début d’échantillonnage de la HBM4 par SK Hynix ne soit pas précisée. Alors que SK Hynix penchait initialement vers l’utilisation de la technologie DRAM 1b pour les couches de mémoire HBM4, la décision de Samsung d’opter pour une production en 1c a entraîné une réévaluation, selon The Elec. SK Hynix collaborera avec TSMC pour fabriquer des matrices de base pour ses modules de mémoire HBM4. Lors du Symposium technologique européen 2024, TSMC a révélé ses plans pour produire ces matrices de base en utilisant ses technologies de processus 12FFC+ avancées et N5. La technologie logique N5 de TSMC permettra une intégration logique plus dense et des pas d’interconnexion plus fins pour placer la mémoire directement sur les CPU et GPU.

Source : www.tomshardware.com